# **General Description**

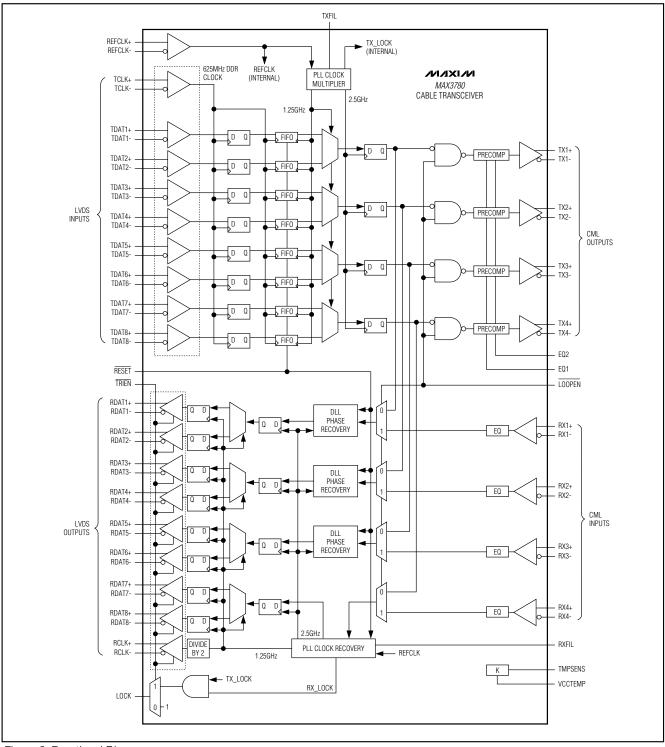

The MAX3780 cable transceiver provides a bidirectional interface of four 2.5Gbps channels over low-cost copper cable or external fiber-optic interface. The transmitter section accepts eight channels of input at 1.25Gbps. An integrated 4-bit FIFO allows retiming of the transmit data to a clean local reference clock. The channels are multiplexed (2:1) into four outputs operating at 2.5Gbps. Preemphasis and equalization provide compensation for losses in low-cost cables up to 3m. The receiver recovers the clock and demultiplexes (1:2) the 2.5Gbps channels into eight 1.25Gbps outputs. Fully integrated phase-locked loops and delay-locked loops recover clock and data from the serial data inputs.

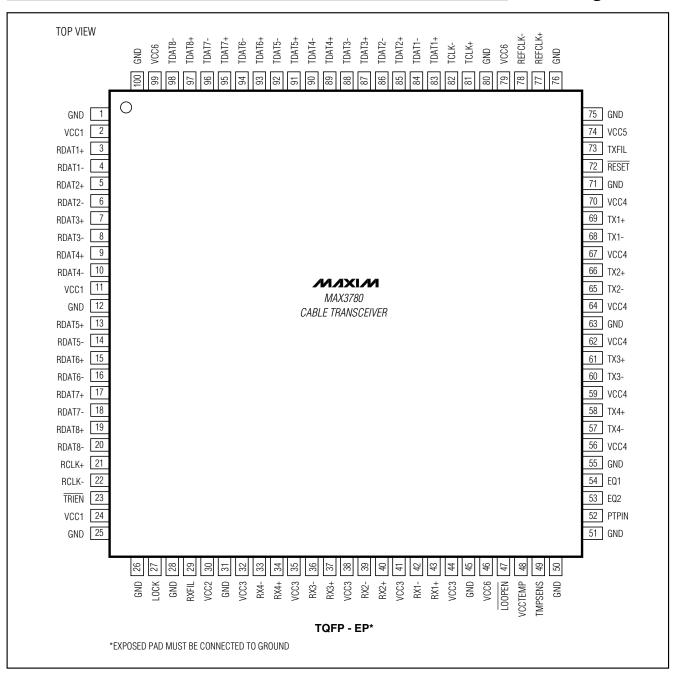

The transceiver IC is available in a compact 100-pin TQFP package with exposed-ground pad and consumes 2.2W.

# Applications

Gigabit Ethernet Cable Backplane Concentration System Interconnects Using Low-Cost Copper Cable

System Interconnects Using Parallel Optics

### \_Features

- Quad 2:1 Channel Serialization

- Quad 1:2 Channel Deserialization

- Sm Link Distance with Low-Cost Copper Cable

- ♦ Better than 10<sup>-16</sup> BER Performance

- ♦ 10Gbps Aggregate Parallel Interface

- System Loopback

- ♦ 1.25Gbps LVDS Synchronous Interface

- ♦ 2.5Gbps CML Serial Cable Interface

- PLL Lock Detect Signal

- Selectable Cable Pre-Emphasis

- Fixed Receive Equalization

### \_Ordering Information

| PART       | TEMP. RANGE  | PIN-PACKAGE  |

|------------|--------------|--------------|

| MAX3780CCQ | 0°C to +70°C | 100 TQFP-EP* |

\*Exposed pad

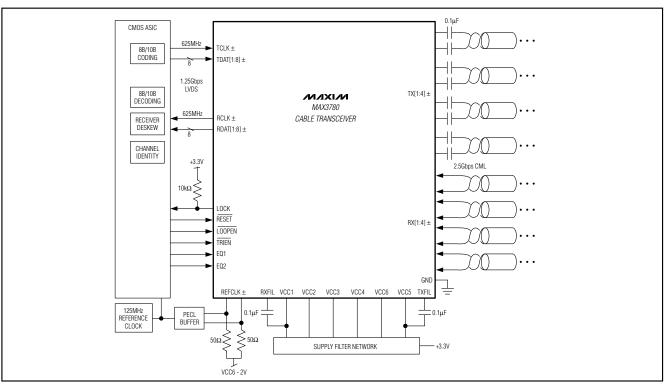

# **Typical Operating Circuit**

###

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (V <sub>CC</sub> 1, V <sub>CC</sub> 2, V <sub>CC</sub> 3, V <sub>CC</sub> 4, |                                  |

|---------------------------------------------------------------------------------------------|----------------------------------|

| V <sub>CC</sub> 5, V <sub>CC</sub> 6, VCCTEMP)                                              | 0.5V to +4.0V                    |

| Continuous CML Output Current                                                               | 10mA to +25mA                    |

| Momentary CML Output Voltage                                                                |                                  |

| (duration < 1 minute, +25°C)                                                                | 0V to (V <sub>CC</sub> + 0.5V)   |

| CML Input Voltage                                                                           | 0.5V to (V <sub>CC</sub> + 0.5V) |

| LVDS Input and Output Voltage                                                               | 0.5V to (V <sub>CC</sub> + 0.5V) |

| TTL Input or Output Voltage          | 0.5V to (V <sub>CC</sub> + 0.5V) |

|--------------------------------------|----------------------------------|

| PECL Input Voltage                   | 0.5V to (V <sub>CC</sub> + 0.5V) |

| TMPSENS, TXFIL, RXFIL Voltage        | 0.5V to (V <sub>CC</sub> + 0.5V) |

| Operating Ambient Temperature Range  | 0°C to +70°C                     |

| Operating Junction Temperature Range | 0°C to +150°C                    |

| Storage Ambient Temperature Range    | 55C° to +100°C                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **DC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0V \text{ to } +3.6V, \text{LVDS} \text{ differential load} = 100\Omega \pm 1\%, \text{ CML differential load} = 100\Omega \pm 1\%, \text{ T}_{A} = 0^{\circ}\text{C} \text{ to } +70^{\circ}\text{C}, \text{ unless otherwise noted}.$  Typical values are at V<sub>CC</sub> = +3.3V and T<sub>A</sub> = +25°C.)

| PARAMETER                           | SYMBOL          | CONDITIONS                                               | MIN                      | ТҮР | MAX                   | UNITS |

|-------------------------------------|-----------------|----------------------------------------------------------|--------------------------|-----|-----------------------|-------|

| Supply Voltage                      | V <sub>CC</sub> | Referenced to GND                                        | 3.0                      | 3.3 | 3.6                   | V     |

| Operating Ambient Temperature       | TA              |                                                          | 0                        | 25  | 70                    | °C    |

| Power Dissipation                   |                 |                                                          | 1.6                      | 2.2 | 3.3                   | W     |

| Supply Current                      | Icc             |                                                          | 533                      | 665 | 916                   | mA    |

| TTL INPUTS AND OUTPUTS              |                 |                                                          |                          |     |                       |       |

| TTL Input High Voltage              | VIH             |                                                          | 2.0                      |     |                       | V     |

| TTL Input Low Voltage               | VIL             |                                                          |                          |     | 0.8                   | V     |

| TTL Input High Current              | IIН             | V <sub>IH</sub> = 2.0V                                   |                          |     | -250                  | μA    |

| TTL Input Low Current               | ١ <sub>IL</sub> | $V_{IL} = 0V$                                            |                          |     | -500                  | μA    |

| TTL Output High Voltage             | VOH             | Open collector, $R_{LOAD} = 10k\Omega$                   | 2.4                      |     |                       | V     |

| TTL Output Low Voltage              | VOL             | $R_{LOAD} = 10k\Omega$                                   |                          |     | 0.4                   | V     |

| PECL INPUTS                         |                 |                                                          |                          |     |                       |       |

| PECL Input High Voltage             |                 | Referenced to V <sub>CC</sub> 6                          | -1165                    |     | -880                  | mV    |

| PECL Input Low Voltage              |                 | Referenced to V <sub>CC</sub> 6                          | -1810                    |     | -1475                 | mV    |

| PECL Input Current                  |                 |                                                          | -10                      |     | +10                   | μA    |

| CML INPUTS (Note 1, Figure 5)       |                 |                                                          |                          |     |                       |       |

| Differential Input Voltage Range    |                 | Total differential signal required to achieve error rate | 200                      |     | 800                   | mVp-p |

| Single-Ended Input Voltage<br>Range |                 | Single-ended range of a differential input signal        | V <sub>CC</sub> -<br>0.5 |     | V <sub>CC</sub> + 0.2 | V     |

| Common-Mode Voltage                 |                 | Inputs open or AC-coupled                                |                          | Vcc |                       | V     |

| Input Impedance                     | RIN             | Differential                                             | 85                       | 100 | 115                   | Ω     |

| CML OUTPUTS (Note 1, Figure 4)      |                 |                                                          |                          |     |                       |       |

| Differential Output Voltage         |                 | 0m channel, EQ1 = 1, EQ2 = 1                             | 400                      | 600 | 800                   |       |

| (Measured at the End of the         |                 | 0.5m channel, EQ1 = 1, EQ2 = 1                           |                          | 540 |                       |       |

| Channel)                            |                 | 1m channel, EQ1 = 1, EQ2 = 0                             |                          | 500 |                       | mVp-p |

| (Note 3)                            |                 | 3m channel, EQ1 = 0, EQ2 = 1                             |                          | 400 |                       | 1     |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0V \text{ to } +3.6V, \text{LVDS} \text{ differential load} = 100\Omega \pm 1\%, \text{ CML differential load} = 100\Omega \pm 1\%, \text{ T}_{\text{A}} = 0^{\circ}\text{C} \text{ to } +70^{\circ}\text{C}, \text{ unless otherwise noted}.$  Typical values are at V<sub>CC</sub> = +3.3V and T<sub>A</sub> = +25°C.)

| PARAMETER                                                                         | SYMBOL              | CONDITIONS                             | MIN   | TYP                      | MAX   | UNITS |

|-----------------------------------------------------------------------------------|---------------------|----------------------------------------|-------|--------------------------|-------|-------|

| Output Common-Mode Voltage                                                        |                     |                                        |       | V <sub>CC</sub> -<br>0.3 |       | V     |

| Differential Output Impedance                                                     | ROUT                |                                        | 85    | 100                      | 115   | Ω     |

| LVDS INPUTS                                                                       |                     |                                        |       |                          |       |       |

| Input Voltage Range                                                               | VI                  | IV <sub>GPD</sub> I < 925mV            | 0     |                          | 2000  | mV    |

| Differential Input Voltage                                                        | IV <sub>ID</sub> I  | IV <sub>GPD</sub> I < 925mV            | 150   |                          | 500   | mV    |

| Differential Input Impedance                                                      | R <sub>IN</sub>     |                                        | 85    | 100                      | 115   | Ω     |

| Input Common-Mode Current                                                         |                     | $V_{OS} = 1.2V$ , inputs tied together |       | -80                      | -200  | μA    |

| LVDS OUTPUTS (Note 2)                                                             |                     |                                        |       |                          |       |       |

| Output High Voltage                                                               | VOH                 |                                        |       |                          | 1.475 | V     |

| Output Low Voltage                                                                | Vol                 |                                        | 0.925 |                          |       | V     |

| Differential Output Voltage                                                       | IV <sub>OD</sub> I  |                                        | 250   |                          | 400   | mV    |

| Change in Magnitude of<br>Differential Output Voltage for<br>Complementary States | ΔIV <sub>OD</sub> I |                                        |       |                          | 25    | mV    |

| Output Offset Voltage                                                             | Vos                 |                                        | 1.125 |                          | 1.275 | V     |

| Change in Magnitude of Output<br>Offset Voltage for<br>Complementary States       | ΔIV <sub>OS</sub> I |                                        |       |                          | 25    | mV    |

| Differential Output Impedance                                                     | R <sub>OD</sub>     |                                        | 80    | 100                      | 120   | Ω     |

| Short-Circuit Current                                                             |                     | Short to supply or ground              |       |                          | 40    | mA    |

| Impedance When Disabled                                                           |                     | $\overline{\text{TRIEN}} = 0$          | 5     | 10                       |       | kΩ    |

Note 1: CML differential signal amplitudes are specified as the total signal across the load (V+ - V-).

Note 2: LVDS output signal amplitudes are specified according to IEEE 1596.3-1996.

**Note 3:** Differential output voltage is production tested for all EQ1 and EQ2 settings. Typical values are the differential peak-to-peak eye opening at the end of the cable.

### AC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0V \text{ to } +3.6V, \text{LVDS} \text{ differential load} = 100\Omega \pm 1\%, \text{ CML differential load} = 100\Omega \pm 1\%, \text{ T}_{A} = 0^{\circ}\text{C} \text{ to } +70^{\circ}\text{C}, \text{ REFCLK} = 125\text{MHz}$ , unless otherwise noted. Typical values are at  $V_{CC} = +3.3V$  and  $T_{A} = +25^{\circ}\text{C}$ .) (Note 4)

| SYMBOL      | CONDITIONS         | MIN             | ТҮР             | MAX                         | UNITS                       |  |  |

|-------------|--------------------|-----------------|-----------------|-----------------------------|-----------------------------|--|--|

|             |                    |                 |                 |                             |                             |  |  |

|             |                    |                 | 625             |                             | MHz                         |  |  |

|             | From TDAT to TX    |                 | 4.5             |                             | ns                          |  |  |

| LVDS INPUTS |                    |                 |                 |                             |                             |  |  |

|             | Relative to REFCLK |                 | ±0.8            |                             | ns                          |  |  |

|             | SYMBOL             | From TDAT to TX | From TDAT to TX | 625   From TDAT to TX   4.5 | 625   From TDAT to TX   4.5 |  |  |

# AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0V \text{ to } +3.6V, \text{LVDS} \text{ differential load} = 100\Omega \pm 1\%, \text{ CML differential load} = 100\Omega \pm 1\%, \text{ T}_{A} = 0^{\circ}\text{C} \text{ to } +70^{\circ}\text{C}, \text{ REFCLK} = 125\text{MHz}$ , unless otherwise noted. Typical values are at  $V_{CC} = +3.3V$  and  $T_{A} = +25^{\circ}\text{C}$ .) (Note 4)

| PARAMETER                       | SYMBOL                          | CONDITIONS                                                        | MIN | ТҮР | MAX | UNITS             |

|---------------------------------|---------------------------------|-------------------------------------------------------------------|-----|-----|-----|-------------------|

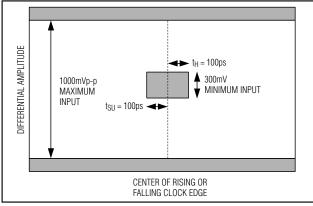

| Setup Time                      | ts∪                             | Figure 1                                                          | 100 |     |     | ps                |

| Hold Time                       | tH                              | Figure 1                                                          | 100 |     |     | ps                |

| CML OUTPUTS                     |                                 |                                                                   |     |     |     |                   |

| Deterministic Jitter            |                                 | (Note 5)                                                          |     | 15  | 25  | ps <sub>p-p</sub> |

| Random Jitter                   |                                 | Wideband jitter with 01 pattern<br>(Note 7)                       | 22  |     | 66  | ps <sub>p-p</sub> |

| Edge Speed                      | t <sub>r</sub> , t <sub>f</sub> | 20% to 80%, measured at transmitter output,<br>(EQ1 = 1, EQ2 = 1) |     | 140 | ps  |                   |

| RECEIVER PARAMETERS             |                                 |                                                                   |     |     |     | •                 |

| Clock Frequency                 |                                 |                                                                   |     | 625 |     | MHz               |

| PLL Lock Time                   |                                 | After valid data applied                                          |     | 525 |     | μs                |

| Receiver Latency                |                                 | From RX to RDAT                                                   |     | 4.3 |     | ns                |

| Jitter Generation               |                                 | (Note 7)                                                          |     | 25  | 66  | ps <sub>p-p</sub> |

| LVDS OUTPUTS                    |                                 |                                                                   |     |     |     |                   |

| Clock Duty-Cycle Distortion     | T <sub>PW</sub>                 | Variation of 50% crossing from ideal time                         | -32 |     | +32 | ps                |

| Deterministic Jitter            |                                 | Measured with K28.5 pattern at RDAT_<br>outputs                   |     | 15  | 50  | ps <sub>p-p</sub> |

| Edge Speed                      | t <sub>r</sub> , t <sub>f</sub> | 20% to 80%                                                        |     | 160 | 250 | ps                |

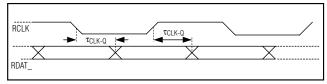

| Clock-to-Data Delay             | τclk-Q                          | Figure 2                                                          | 268 | 400 | 532 | ps                |

| CML INPUTS                      | •                               |                                                                   |     |     |     | •                 |

| High-Frequency Jitter Tolerance |                                 | (Note 6)                                                          | 220 | 300 |     | ps <sub>p-p</sub> |

**Note 4:** AC characteristics are guaranteed by design and characterization.

Note 5: Deterministic jitter (DJ) and differential output signal measured with K28.5 at TX\_ pins.

**Note 6:** High-frequency jitter comprised of 164ps<sub>p-p</sub> of deterministic jitter, 1.6ps<sub>RMS</sub> random jitter, and the remaining as 5MHz sinusoidal jitter.

Note 7: Peak-to-peak random jitter is  $16.4 \times RMS$  jitter for a jitter probability of  $10^{-16}$ .

Figure 1. LVDS Receiver Input Eye Mask

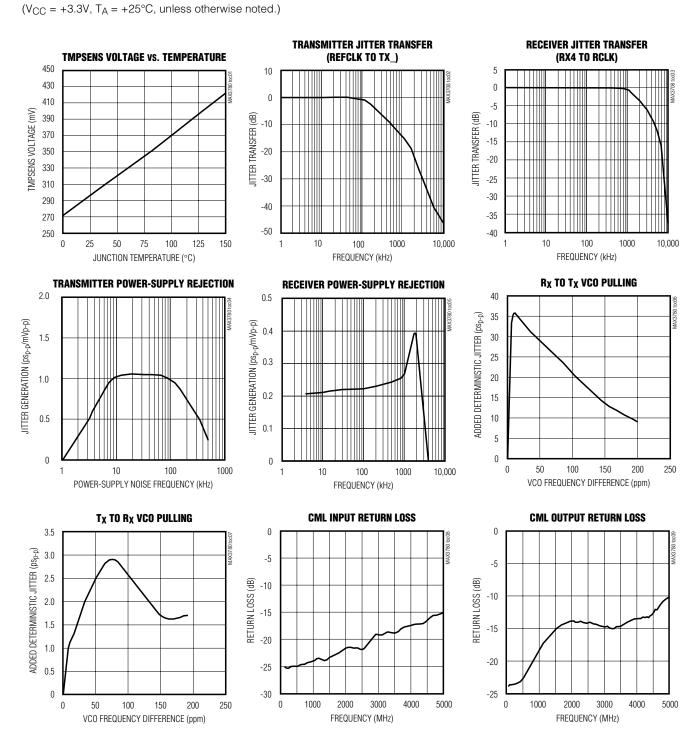

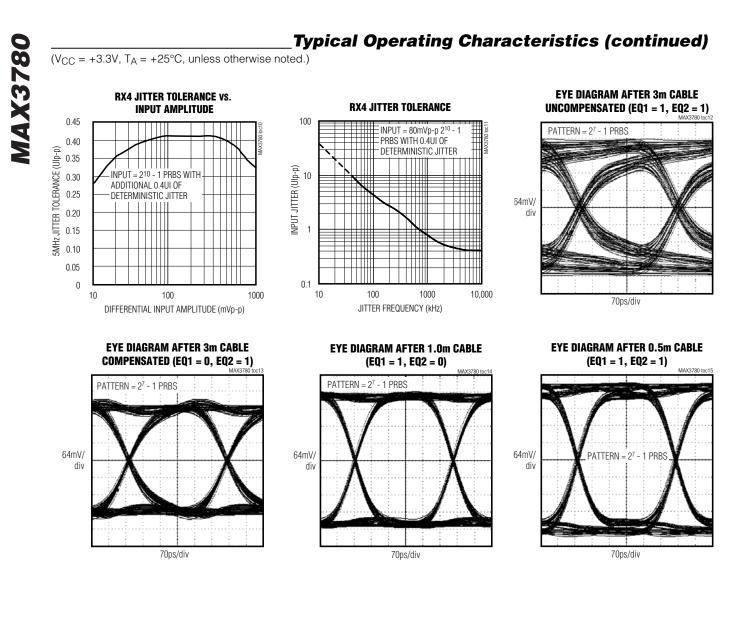

# **Typical Operating Characteristics**

**MAX3780**

M/IXI/M

# **Pin Description**

| PIN                                                                  | NAME                | FUNCTION                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 12, 25, 26, 28, 31,<br>45, 50, 51, 55, 63, 71,<br>75, 76, 80, 100 | GND                 | Supply Ground                                                                                                                                                                                                                                                                                                                                     |

| 2, 11, 24                                                            | VCC1                | +3.3V Supply for Receiver, LVDS Data and Clock Outputs, and Digital Receiver Functions                                                                                                                                                                                                                                                            |

| 3, 5, 7, 9, 13, 15, 17,<br>19                                        | RDAT1+ to<br>RDAT8+ | Positive Parallel-Data Outputs, LVDS                                                                                                                                                                                                                                                                                                              |

| 4, 6, 8, 10, 14, 16, 18,<br>20                                       | RDAT1- to<br>RDAT8- | Negative Parallel-Data Outputs, LVDS                                                                                                                                                                                                                                                                                                              |

| 21                                                                   | RCLK+               | Positive 625MHz Recovered Clock, LVDS. Parallel-data outputs are clocked on both the rising and falling edge of the clock.                                                                                                                                                                                                                        |

| 22                                                                   | RCLK-               | Negative 625MHz Recovered Clock, LVDS. Parallel-data outputs are clocked on both the rising and falling edge of the clock.                                                                                                                                                                                                                        |

| 23                                                                   | TRIEN               | Three-State Enable, TTL Input. Setting $\overline{\text{TRIEN}}$ low forces the LVDS outputs into a high-<br>impedance state and the LOCK pin to a logical '1'. CML outputs are not affected by<br>$\overline{\text{TRIEN}}$ . Internally pulled high through 15k $\Omega$ .                                                                      |

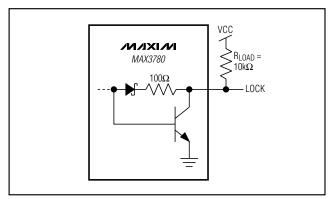

| 27                                                                   | LOCK                | Lock Status Indicator, TTL Output. This output goes high when the transmit PLL, receiver PLL, and receiver DLLs are in lock. Because this output is open-collector TTL, it requires an external 10k $\Omega$ pullup resistor to V <sub>CC</sub> . The LOCK pins from multiple MAX3780s can be connected in parallel to form a single LOCK signal. |

| 29                                                                   | RXFIL               | Receiver Loop Filter Connection. Connect a 0.1µF capacitor between RXFIL and VCC2.                                                                                                                                                                                                                                                                |

| 30                                                                   | VCC2                | +3.3V Supply for Receiver VCO, Analog Receiver Functions, and External Loop Filter<br>Connection                                                                                                                                                                                                                                                  |

| 32, 35, 38, 41, 44                                                   | VCC3                | +3.3V Supply for CML Inputs                                                                                                                                                                                                                                                                                                                       |

| 33, 36, 39, 42                                                       | RX4- to<br>RX1-     | Negative Serial Input, CML                                                                                                                                                                                                                                                                                                                        |

| 34, 37, 40, 43                                                       | RX4+ to<br>RX1+     | Positive Serial Input, CML                                                                                                                                                                                                                                                                                                                        |

| 46, 79, 99                                                           | VCC6                | +3.3V Supply for LVDS Inputs, FIFO, Multiplexer, and PECL REFCLK Input                                                                                                                                                                                                                                                                            |

| 47                                                                   | LOOPEN              | Loopback Enable, TTL input. Force low to enable system loopback. Internally pulled high through 15k $\Omega.$                                                                                                                                                                                                                                     |

| 48                                                                   | VCCTEMP             | +3.3V Supply for TMPSENS. Connect to ground to disable the temperature-sensing circuit.                                                                                                                                                                                                                                                           |

| 49                                                                   | TMPSENS             | Junction Temperature Sensor. Analog output corresponding to the junction temperature of the die. Leave open for normal use.                                                                                                                                                                                                                       |

| 52                                                                   | PTPIN               | Reserved for Maxim Use. Connect to ground for normal operation.                                                                                                                                                                                                                                                                                   |

| 53                                                                   | EQ2                 | Transmit Equalizer Control Input #2, TTL. Refer to Table 1 for setting transmitter precompensation. Internally pulled high.                                                                                                                                                                                                                       |

| 54                                                                   | EQ1                 | Transmit Equalizer Control Input #1, TTL. Refer to Table 1 for setting transmitter precompensation. Internally pulled high.                                                                                                                                                                                                                       |

| 56, 59, 62, 64, 67, 70                                               | VCC4                | +3.3V Supply for CML Outputs                                                                                                                                                                                                                                                                                                                      |

**MAX3780**

| PIN                               | NAME                | FUNCTION                                                                                                                    |

|-----------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 57, 60, 65, 68                    | TX4- to<br>TX1-     | Negative Serial Output, CML                                                                                                 |

| 58, 61, 66, 69                    | TX4+ to<br>TX1+     | Positive Serial Output, CML                                                                                                 |

| 72                                | RESET               | Reset Input, TTL. Connect low for >80ns to reset FIFO and receiver components. Internally pulled high through $15k\Omega$ . |

| 73                                | TXFIL               | Transmitter Loop Filter Connection. Connect a 0.1µF capacitor between TXFIL and VCC5.                                       |

| 74                                | VCC5                | +3.3V Supply for Transmitter VCO, Analog Transmitter Functions, and External Loop Filter Connection                         |

| 77                                | REFCLK+             | Positive Reference Clock Input, PECL                                                                                        |

| 78                                | REFCLK-             | Negative Reference Clock Input, PECL                                                                                        |

| 81                                | TCLK+               | Positive Clock Input for Transmitter Input Data, LVDS                                                                       |

| 82                                | TCLK-               | Negative Clock Input for Transmitter Input Data, LVDS                                                                       |

| 83, 85, 87, 89, 91, 93,<br>95, 97 | TDAT1+ to<br>TDAT8+ | Positive Parallel Data Inputs, LVDS                                                                                         |

| 84, 86, 88, 90, 92, 94,<br>96, 98 | TDAT1- to<br>TDAT8- | Negative Parallel Data Inputs, LVDS                                                                                         |

# **Pin Description (continued)**

# **Detailed Description**

The MAX3780 cable transceiver uses four 2:1 muxes and four 1:2 demuxes to simplify backplane routing. The serial transceiver interface can either be a fiber module or up to 3m of low-cost, twisted-pair copper cable. This bidirectional interface provides low-voltage differential signaling (LVDS) interfaces at the 1.25Gbps parallel inputs and outputs. The serial data inputs and outputs utilize current-mode logic (CML) structures. An integrated PLL recovers the clock from the incoming serial data, as well as retimes the received data.

The serial interface uses both precompensation as well as equalization to allow high-speed transmission through up to 3m of copper cable while maintaining a BER <  $10^{-16}$ . The compensation/equalization circuits are optimized for short cables, 0.5m cables, 1m cables, or 3m cables. TTL inputs are provided to select the amount of precompensation.

### **LVDS** Inputs and Outputs

The MAX3780 parallel interface includes eight differential data inputs at 1.25Gbps, one half-rate differential clock input at 625MHz, eight differential data outputs at 1.25Gbps, and one half-rate differential clock output at 625MHz. All parallel inputs and outputs are LVDS compatible to minimize power dissipation, speed transition time, and improve noise immunity. The LVDS outputs go into a high-impedance state when TRIEN is forced low. This simplifies system checks by allowing vectors to be forced on the LVDS outputs. The LVDS outputs also have short-circuit protection in case of shorts to VCC or GND.

#### **PLL Clock Multiplier**

The PLL clock multiplier uses the 125MHz reference clock to synthesize 1.25GHz and 2.5GHz clocks used to synchronize the transmitter functions. The reference clock is also used to aid frequency acquisition in the receiver. The 125MHz input signal at REFCLK requires a duty cycle between 40% and 60%. To achieve proper jitter performance and BER benchmarks, it is critical to use a high-quality, low-jitter reference clock. See the *Reference Clock Requirements* table for more information.

#### **Bit-Interleaved Multiplexer/Demultiplexer** The MAX3780 uses bit interleaving to multiplex the parallel data and bit deinterleaving to demultiplex the seri-

allel data and bit deinterleaving to demultiplex the serial data. After serial transmission, the channel assignment of the parallel outputs is random for each serial channel. In other words, there is a 50% chance that RDAT1 = TDAT1 and RDAT2 = TDAT2 and a 50% chance that RDAT1 = TDAT2 and RDAT2 = TDAT1. Because the MAX3780 does not perform channel assignment, other circuitry must handle this task.

**Quad 2.5Gbps Cable Transceiver**

Figure 3. Functional Diagram

**MAX3780**

9

# Table 1. Setting the CML OutputPrecompensation

| RECOMMENDED<br>CHANNEL        | PRECOMPENSATION<br>VALUE | EQ1 | EQ2 |

|-------------------------------|--------------------------|-----|-----|

| Extended Range                | 30%                      | 0   | 0   |

| 3m Cable                      | 20%                      | 0   | 1   |

| 1m Cable                      | 10%                      | 1   | 0   |

| 0.5m Cable or<br>Fiber Module | Off                      | 1   | 1   |

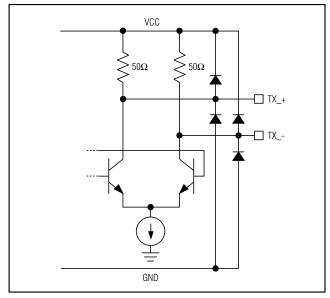

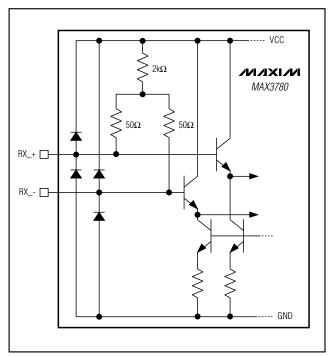

Figure 4. Simplified CML Output Structure

### **PLL Clock Recovery**

The phase-locked loop recovers a synchronous clock signal from the incoming serial data on RX4. This recovered clock is then used to retime all four channels of incoming serial data before demultiplexing. Phase alignment on channels RX1, RX2, and RX3 is achieved by using delay-locked loops. The typical loop bandwidth of the PLL clock recovery circuit is 1.5MHz.

### **Delay-Locked Loop (DLL) Phase Recovery**

The delay-locked loops in the RX1, RX2, and RX3 receive path are used to phase align the incoming data to the clock generated by the PLL. Because all serial channels originate from the same source and travel down the same cable, it is assumed that the low-frequency jitter on channel 4 is common to all channels. This allows the PLL to maintain frequency/phase align-

ment, and the DLLs only serve as adjustable delay lines to allow for different channels to have different (static) phase relationships.

**CML Outputs with Precompensation** The serial outputs of the MAX3780 (TX1–TX4) are CML compatible. These outputs offer the best combination of low power dissipation, performance, and external component count. AC-coupling capacitors should always be used to provide immunity to common-mode voltage mismatches. The CML output structure is shown in Figure 4. For more information, refer to the applications note HFAN 01.0 *Introduction to LVDS*, *PECL, and CML*. Table 1 gives the amount of compensation for different EQ1 and EQ2 settings.

The CML data outputs have adjustable precompensation to compensate for cable and PC board trace losses. The cable and PC board traces have skin-effect and dielectric losses that attenuate high frequencies more than low frequencies. The precompensation FIR filter does the inverse. It attenuates low frequencies and boosts high frequencies. If precompensation is chosen to match the channel attenuation, the data at the end of the cable will be equalized.

### **CML Inputs with Equalization**

The CML input structure, shown in Figure 5, provides low power dissipation and excellent performance. The CML inputs have integrated  $50\Omega$  termination resistors, reducing the external component count required for interfacing.

The CML inputs of the MAX3780 (RX1–RX4) provide equalization to further compensate for cable losses. The equalization circuit will typically add about 2dB of boost at 2GHz.

### **Lock Detection**

The LOCK output indicates the state of both the transmitter and receiver PLLs. For lock detect to be asserted high, both the transmitter and receiver internal-lock indicators must be high for 394µs. The internal lock signals go high once frequency lock has been achieved. For LOCK to be asserted low, either the transmitter or receiver internal-lock indicators must be low for a minimum of 1053µs. LOCK is also asserted low when RESET is forced low. LOCK will stay low for a minimum of 394µs. For the lock detector to function properly, there must be data transitions at the RX4 input and a valid reference clock input. **Note:** The LOCK output is not an accurate indicator of signal presence at the receiver inputs. With no data input, the LOCK output can be high, low, or toggling.

Figure 5. CML Input Structure

Figure 6. LOCK Output Structure

### **RESET** Input

Approximately 10ms or longer after power-up, the RESET input should be asserted low. RESET must be held low for a minimum of four reference clock cycles for it to be properly asserted. RESET is used to reset the lock state, FIFO clock logic, and delay-lock loops.

#### **Temperature Sensor**

To aid in evaluation of thermal performance, a temperature sensor is incorporated into the MAX3780. The temperature sensor may be powered on or off regardless of the state of the rest of the chip. The VCCTEMP pin provides supply voltage for the temperature sensor circuit. The TMPSENS output is designed to output a voltage proportional to the die junction temperature (1mV per Kelvin). The temperature of the die can be estimated as:

$$T(^{\circ}C) \approx V_{\text{TEMPSENS}}(mV) \times \frac{1^{\circ}C}{mV} - 273^{\circ}C$$

### Applications Information

#### **BER Calculation**

Digital transmission systems will always, given enough time, have errors. This is due to the random nature of both voltage noise and timing noise, or jitter. In today's high performance digital transmission systems, we often try to measure bit error ratios (BERs) of fewer than 1 error every 10,000,000,000 bits (BER<10<sup>-10</sup>). Measuring such low error rates can prove to be problematic, since even at high data rates, the testing time required to obtain statistically significant results becomes impractical. (For more information, refer to HFTA-05.0 *Statistical Confidence Levels for Calculating Error Probability.*)

The MAX3780 serial interface operates at 2.5Gbps and is designed to operate with a BER better than 10<sup>-16</sup> (1 error every 10,000,000,000,000 bits). This will give, on average, one error every 46 days on each 2.5Gbps channel. It is practically impossible to directly test such a low BER. For this reason, we turn to mathematics to ensure that this incredible BER is met.

The thermal noise in the MAX3780 serial channel is low (<1mV<sub>RMS</sub> in the CML receiver). The dominant voltage noise in the serial channel is due to crosstalk. The remaining impairments are various types of timing jitter due to clock nonidealities and data-dependant jitter. In this section, all calculations will be done in the time domain (similar to the draft technical report by ANSI T11.2, Project 1230, *Fibre Channel—Methodologies for Jitter Specification*) where timing jitter is applied directly and voltage noise is converted into an equivalent timing jitter. The equation relating timing jitter to error rate is below:

$$1UI = \Sigma DJ_{p-p} + \alpha \times \sqrt{\Sigma RJ^2_{RMS}}$$

###

|                                | DETERMINIST         | IC COMPONENTS          | RANDOM C                         | OMPONENTS                           |

|--------------------------------|---------------------|------------------------|----------------------------------|-------------------------------------|

| PARAMETER                      | TYPICAL<br>(mUlp-p) | WORST-CASE<br>(mUlp-p) | TYPICAL<br>(mUI <sub>RMS</sub> ) | WORST-CASE<br>(mUI <sub>RMS</sub> ) |

| Reference Clock—Random         |                     |                        | 0.19                             | 0.38                                |

| Reference Clock—Deterministic  | 5                   | 10                     |                                  |                                     |

| Transmitter—Random             |                     |                        | 3.25                             | 10                                  |

| Transmitter—Oscillator Pulling | 8.75                | 23.75                  |                                  |                                     |

| Transmitter—Supply Noise       | 2.5                 | 7.5                    |                                  |                                     |

| Transmitter—Output Stage       | 37.5                | 62.5                   |                                  |                                     |

| Channel—Cable Losses           | 50                  | 112.5                  |                                  |                                     |

| Channel—Crosstalk              | 28                  | 56                     |                                  |                                     |

| Channel—Mismatched Load        | 12.5                | 25                     |                                  |                                     |

| Receiver—VCO Phase Noise       |                     |                        | 3.75                             | 10                                  |

| Receiver—Input-Referred Noise  |                     |                        | 1.25                             | 2.5                                 |

| Receiver—Sampling Offset       | 187.5               | 387.5                  |                                  |                                     |

| Receiver—Oscillator Pulling    | 7.5                 | 15                     |                                  |                                     |

| Receiver—Supply Noise          | 6.25                | 18.75                  |                                  |                                     |

| TOTALS =                       | 345.5               | 718.5                  | 5.12                             | 14.37                               |

|                                | TYPICAL             | WORST-CASE             |                                  |                                     |

| ALPHA =                        | 127.8               | 19.6                   |                                  |                                     |

| BER =                          | ~0                  | 5.7 × 10-23            |                                  |                                     |

### Table 2. Summary of Jitter Parameters Contributing to the BER Calculation

Deterministic jitter and receiver sampling offset effectively reduce the amount of time that the receiver can sample without error. Errors occur at a rate determined by  $\alpha$ :

$$\alpha = \frac{1 - \Sigma D J_{p-p}}{\sqrt{\Sigma R J_{BMS}^2}}$$

An  $\alpha$  >16.4 corresponds to a BER < 10<sup>-16</sup>. Refer to Maxim applications note HFAN-4.0.2 *Converting Between RMS and Peak-to-Peak Jitter at a Specified BER*.

For a discussion of deterministic jitter and random jitter and the characteristics of each, refer to Maxim applications note HFAN-4.0.3 *Jitter in Digital Communication Systems, Part 1.*

Table 2 shows the deterministic and random components used in the BER calculation for the MAX3780. Typical and worst-case numbers are presented. The worst-case estimate represents a BER with greater than 6-sigma margin. Many of the worst-case components are uncorrelated variables that are taken to their individual 6-sigma limits.

In summary, the predicted worst-case BER =  $10^{-20}$ . A typical channel will operate error free.

All transmitter and channel jitter components are compared to the jitter tolerance of the receiver by translating the components to equivalent phase error in the receiver. Low-frequency jitter components are tracked by the receive PLL, and therefore contribute little to the phase error. High-frequency jitter components (beyond the loop bandwidth of the receiver) are not tracked by the receiver PLL and therefore directly translate to phase error. The phase error transfer function is essentially equivalent to the inverse of the jitter tolerance versus frequency with the high-frequency portion normalized to unity.

#### Reference Clock—Random

A maximum random jitter of 15ps<sub>RMS</sub> for frequencies less than 5kHz is stated as a requirement for the reference clock in the *Reference Clock Requirements* section. Translating this to the phase error of the receiver gives 75fs<sub>RMS</sub> (0.19mUI<sub>RMS</sub>) typical and 150fs<sub>RMS</sub> (0.38mUI<sub>RMS</sub>) worst-case.

#### Reference Clock—Deterministic

A maximum deterministic jitter of  $20p_{p-p}$  for frequencies greater than 5kHz is stated as a requirement for the reference clock in the *Reference Clock Requirements* section. Combining the low-pass jitter transfer of the transmitter and the high-pass phase error transfer of the receiver results in a bandpass transfer function. For design margin, it is assumed that this deterministic jitter is within the bandpass frequency range. The typical deterministic component is  $2p_{p-p}$  (5mUlp-p) and the worst-case entry is  $4p_{p-p}$  (10mUlp-p).

#### Transmitter—Random

This is the random jitter that results from the transmitter VCO phase noise and is an AC parameter guaranteed in the *AC Electrical Characteristics* table. Typical measured numbers are 1.3ps<sub>RMS</sub> (3.3mUI<sub>RMS</sub>) and the worst-case specification is 4.0ps<sub>RMS</sub> (10mUI<sub>RMS</sub>).

#### Transmitter—Deterministic

#### 1) Oscillator Pulling

The transmitter and receiver integrated LC oscillators when running at small frequency differences will beat with each other at a rate equivalent to the frequency difference between the oscillators. *Typical Operating Characteristic* plot RX to TX VCO PULLING shows the typical transmitter jitter versus frequency difference. When referred to the phase error transfer, the deterministic jitter is typically 3.5psp-p (8.75mUlp-p) and 9.5psp-p (23.75mUlp-p) worst-case.

#### 2) Supply Noise

Noise on the power supply will modulate the transmit PLL output according to the typical transfer curve shown in the *Typical Operating Characteristic* plot TRANSMITTER POWER-SUPPLY REJECTION. Combining this transfer function with the phase error transfer of the receiver results in a band-pass characteristic. At the peak of this band pass, the typical transfer is 100fs/mV and the worst-case transfer is 300fs/mV. Making the worst-case assumption that all the supply noise is at this peak with a value of 10mV results in typically 1psp-p (2.5mUIp-p) and worst-case 3psp-p (7.5mUIp-p).

#### 3) Output Stage

Finite bandwidth and pulse-width distortion in the serial transmitter can cause deterministic jitter in the serial data stream. Characterization and simulation results tell us the deterministic jitter is typically 15psp-p (37.5mUlp-p) and 25psp-p (62.5mUlp-p) worst-case.

#### Channel—Deterministic

#### 1) Cable Losses

The frequency-dependent skin-effect and dielectric losses in the cable (and PC board traces) will cause data-dependent jitter (also known as intersymbol interference). Adjustable transmit precompensation and fixed receiver boost is used to reduce the cable-induced jitter. However, there will always be some uncompensated jitter due to the cable and PC board trace losses. Characterization and simulation results tell us the deterministic jitter is typically  $20p_{p-p}$  (50mUlp-p) and  $45p_{p-p}$  (112.5mUlp-p) worst-case.

2) Crosstalk

The MAX3780 channel requirements allow for crosstalk of up to 5% to be present at the RX inputs. This is a peak-to-peak voltage measurement which refers to 5% of the transmitter amplitude. Characterization and simulation results tell us the deterministic jitter due to crosstalk is typically 11.2psp-p (28mUlp-p) and 22.4psp-p (56mUlp-p) worst-case.

3) Mismatched Load Jitter

Incorrect impedances in PC board traces, connectors, cables, and terminations can cause reflections that can, in turn, cause deterministic jitter. These effects are more pronounced on short cables (less attenuation of the reflection) where timing margins are highest. While measurements already account for mistermination effects, we have allocated an additional fixed budget for jitter induced by reflections. Characterization and simulation results tell us the deterministic jitter due to load mismatch is typically 5ps<sub>p-p</sub> (12.5mUIp-p) and 10ps<sub>p-p</sub> (25mUIp-p) worst-case.

#### Receiver—Random

#### 1) VCO Phase Noise

This is the random jitter that results from the receiver VCO phase noise and is an AC parameter guaranteed in the *AC Electrical Characteristics* table. Typical measured numbers are 1.5psRMS (3.75mUIRMS) and the worst-case specification is 4psRMS (10mUIRMS).

2) Input-Referred Noise

All electronic circuits generate random noise. The input-referred noise voltage of the CML RX inputs is < 0.5mV<sub>RMS</sub>. This will contribute <1ps<sub>RMS</sub> jitter. In the BER calculation, it is assumed the jitter is typically 0.5ps<sub>RMS</sub> (1.25mUI<sub>RMS</sub>) and 1ps<sub>RMS</sub> (2.5mUI<sub>RMS</sub>) worst-case.

#### Receiver—Deterministic

#### 1) Sampling Offset

The peak-to-peak sampling offset in the receiver is equal to 1UI minus the jitter tolerance minus the random jitter of the receiver. Removal of the random jitter is necessary since receiver VCO Phase Noise in Table 2 accounts for this. For simplicity, the random jitter portion will be assumed to be the typical measured value of  $25ps_{p-p}$  (62.5mUIp-p). Using the numbers from the AC parameter electrical table, the typical sampling offset is calculated to be 187.5mUIp-p and the worst-case is 387.5mUIp-p.

#### 2) Oscillator Pulling

The transmitter and receiver integrated LC oscillators, when running at small frequency differences, will beat with each other at a rate equivalent to the frequency difference between the oscillators. *Typical Operating Characteristic* plot TX to RX VCO PULLING shows the typical receiver jitter versus frequency difference. Typically the receiver oscillator pulling jitter is 3psp-p (7.5mUlp-p) and worst-case is 6psp-p (15.0mUlp-p).

### 3) Supply Noise

Noise on the power supply will modulate the receive PLL sampling point according to the typical transfer curve shown in *Typical Operating Characteristic* plot RECEIVER POWER-SUPPLY REJECTION. Using a typical transfer of 250fs/mV and a worst-case transfer of 750fs/mV with 10mV of supply noise results in 2.5psp-p (6.25mUlp-p) and 7.5psp-p (18.75mUlp-p) respectively.

#### Low-Voltage Differential Signal (LVDS) Inputs/Outputs

The MAX3780 has LVDS inputs and outputs for interfacing with high-speed digital circuitry. All LVDS inputs and outputs are compatible with the IEEE-1596.3 LVDS specification. This technology uses 250mV to 400mV differential low-voltage amplitudes to achieve fast transition times, minimize power dissipation, and improve noise immunity. For proper operation, the parallel clock and data LVDS outputs (RCLK+, RCLK-, RDAT\_+, RDAT\_-) require 100 $\Omega$  differential DC terminations between the inverting and noninverting outputs. Do not terminate these outputs to ground. The parallel data LVDS inputs (TCLK+, TCLK-, TDAT\_+, TDAT\_-) are internally terminated with 100 $\Omega$  differential input resistance and therefore do not require external termination.

The LVDS inputs must be biased for proper operation. DC-coupling LVDS outputs and inputs together provides sufficient biasing. When interfacing to laboratory test equipment, AC-coupling cannot be used. A signal source with DC offset must be used.

#### **Layout Techniques**

For best performance, use good high-frequency layout techniques. Filter voltage supplies, keep ground connections short, and use multiple vias where possible. Use controlled-impedance  $50\Omega$  transmission lines to interface with the MAX3780 high-speed inputs and outputs.

Place power-supply decoupling as close to  $V_{CC}$  as possible. To reduce feedthrough, take care to isolate the input signals from the output signals.

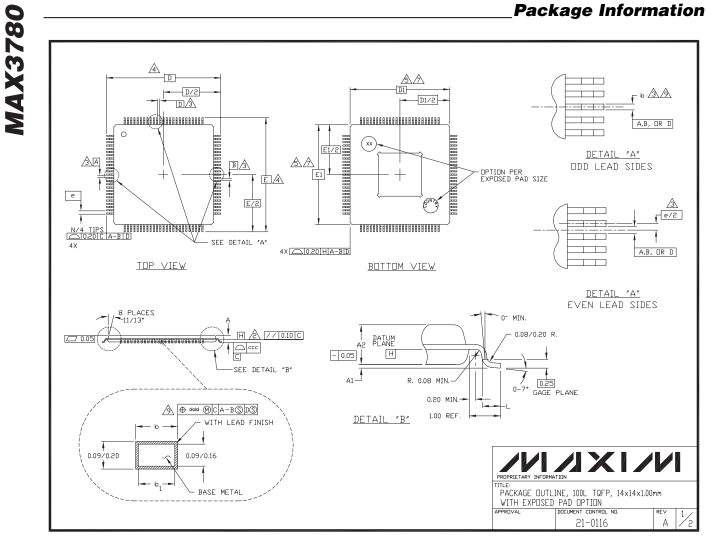

### Exposed-Pad (EP) Package

The exposed-pad 100-pin TQFP-EP incorporates features that provide a very low thermal resistance path for heat removal from the IC. The pad is electrical ground on the MAX3780 and must be soldered to the circuit board for proper thermal and electrical performance.

### **Channel Requirements**

| PARAMETER             | SYMBOL     | CONDITIONS                                                                                                                                   | MIN             | ТҮР | MAX | UNITS |

|-----------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-------|

| Impedance             |            | Differential                                                                                                                                 |                 | 100 |     | Ω     |

|                       |            | f = 1GHz, 3m channel                                                                                                                         | 4.0             | 5.0 | 6.0 |       |

| Through Loss at 1GHz  | (S12, S21) | f = 1GHz, 1m channel                                                                                                                         | 1.5             | 2.4 | 3.2 | dB    |

|                       |            | f = 1GHz, 0.5m channel                                                                                                                       | 1.0             | 1.7 | 2.6 |       |

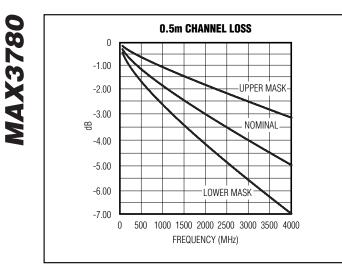

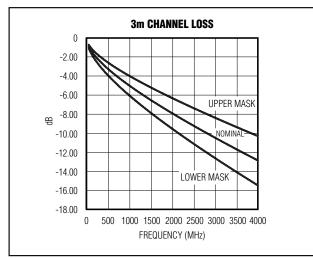

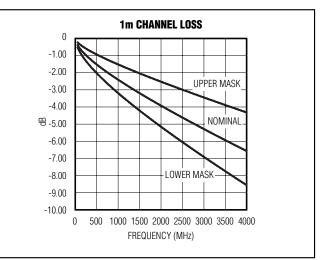

| Wideband Through Loss | (S12, S21) |                                                                                                                                              | See Figures 7–9 |     |     |       |

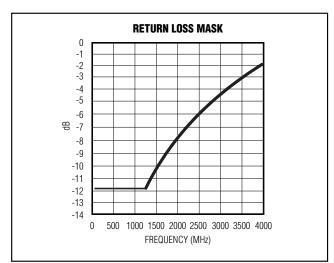

| Return Loss at 1GHz   | (S11, S22) |                                                                                                                                              |                 |     | -12 | dB    |

| Wideband Return Loss  | (S11, S22) |                                                                                                                                              | See Figure 10   |     |     |       |

| Channel Crosstalk     |            | % of signal at aggressor. Near-end and far-end aggressors driven with 100ps (20% to 80%) edges. End of channel terminated with $100\Omega$ . |                 |     | 5   | %     |

### **Reference Clock Requirements**

| PARAMETER                  | SYMBOL | CONDITIONS                                                                                       | MIN  | ТҮР | MAX  | UNITS             |

|----------------------------|--------|--------------------------------------------------------------------------------------------------|------|-----|------|-------------------|

| REFCLK Frequency           |        |                                                                                                  |      | 125 |      | MHz               |

| REFCLK Frequency Tolerance |        |                                                                                                  | -100 |     | +100 | ppm               |

| REFCLK Duty Cycle          |        |                                                                                                  | 40   |     | 60   | %                 |

| REFCLK Jitter              |        | f < 5kHz (jitter assumed Gaussian)                                                               |      |     | 240  | ps <sub>p-p</sub> |

|                            |        |                                                                                                  |      |     | 15   | psrms             |

|                            |        | f > 5kHz (jitter is assumed deterministic,<br>caused by power-supply noise and buffer<br>jitter) |      |     | 20   | ps <sub>p-p</sub> |

### **Parallel Fiber Module Requirements**

| PARAMETER                      | SYMBOL | CONDITIONS                                                                          | MIN | ТҮР | MAX | UNITS             |

|--------------------------------|--------|-------------------------------------------------------------------------------------|-----|-----|-----|-------------------|

| Differential Input Impedance   | RIN    |                                                                                     | 80  | 100 | 120 | Ω                 |

| Transmitter Input Sensitivity  |        |                                                                                     |     |     | 300 | mVp-p             |

| Total Jitter Generation        |        | Deterministic and random jitter, peak-to-<br>peak, (DJ + 16.4 × RJ <sub>RMS</sub> ) |     |     | 80  | ps <sub>p-p</sub> |

| Receiver Data Output Amplitude |        | Differential                                                                        | 300 |     | 800 | mVp-p             |

| Differential Output Impedance  | Rout   |                                                                                     | 80  | 100 | 120 | Ω                 |

| Channel-to-Channel Crosstalk   |        |                                                                                     |     |     | 5   | %                 |

Figure 7. 0.5m Channel Loss Mask

Figure 9. 3.0m Channel Loss Mask

Figure 8. 1.0m Channel Loss Mask

Figure 10. Channel Input Return Loss Mask

\_Pin Configuration

**MAX3780**

## **Chip Information**

TRANSISTOR COUNT: 15,270 PROCESS: Bipolar

### Package Information (continued)

# NDTES:

- 1. ALL DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2: DATUM PLANE H LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

- 3. DATUM A-B AND D TO BE DETERMINED AT CENTERLINE BETWEEN LEADS WHERE LEADS EXITS PLASTIC BODY AT DATUM PLANE H.

- 4. TO BE DETERMINED AT SEATING PLANE C.

- DIMENSIONS D1 AND E1 D0 NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION IS 0.254mm ON D1 AND E1 DIMENSIONS.

- 6. "N" IS THE TOTAL NUMBER OF TERMINALS.

- THESE DIMENSIONS TO BE DETERMINED AT DATUM PLANE

- 8. THE TOP OF PACKAGE IS SMALLER THAN THE BOTTOM OF PACKAGE BY 0.15mm.

- DIMENSIONS & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE & DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT.

- 10. CONTROLLING DIMENSION: MILLIMETER

- 11. MAXIMUM ALLOWABLE DIE THICKNESS TO BE ASSEMBLED IN THIS PACKAGE FAMILY IS 0.50mm.

- 12. THIS OUTLINE IS NOT YET JEDEC REGISTERED.

- A1 IS DEFINED AS THE DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT OF THE PACKAGE BODY.

- 14. EXPOSED DIE PAD SHALL BE COPLANAR WITH BOTTOM OF PACKAGE WITHIN 0.05mm.

- 15. METAL AREA OF EXPOSED DIE PAD SHALL BE WITHIN 0.30mm OF THE NOMINAL DIE PAD SIZE.

- 16. COUNTRY OF ORIGIN MUST BE MARKED ON THE PACKAGE.

| S<br>Y         | ALL DIMENSIONS ARE IN MILLIMETERS |            |      |        |  |

|----------------|-----------------------------------|------------|------|--------|--|

| B<br>L         |                                   | N          |      |        |  |

|                | MIN.                              | NDM.       | MAX. | T<br>E |  |

| A              | $\sim$                            | ~~         | 1.20 |        |  |

| A <sub>1</sub> | 0.05                              | *          | 0.15 | 13     |  |

| Ae             | 0.95                              | 1.00       | 1.05 |        |  |

| D              |                                   | 4          |      |        |  |

| $\mathbb{D}_1$ |                                   | 7,8        |      |        |  |

| E              |                                   | 4          |      |        |  |

| E1             |                                   | 7,8        |      |        |  |

| L              | 0.45                              | 0.60       | 0.75 |        |  |

| Ν              | 100                               |            |      |        |  |

| е              |                                   |            |      |        |  |

| b              | 0.17                              | 0.22       | 0.27 | 9      |  |

| b1             | 0.17                              | 0.20       | 0.23 |        |  |

| ссс            | $\sim$                            | $\sim$     | 0.08 |        |  |

| ddd            | ~~<br>~~                          | The second | 0.08 |        |  |

19

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

© 2001 Maxim Integrated Products

Printed USA

**MAXIM** is a registered trademark of Maxim Integrated Products.